Linux OS

The dual core ARM A9 processor runs the Linux operating system Linaro (Ubuntu, optimized for embedded devices). The OS and filesystems are stored on a SD card. With the Linux OS the Panoradio offers comparable possibilities as a PC (although the Zynq has not as much computing power). The SDR can run any general purpose software for Linux. For this project, e.g. I compiled Fldigi for demodulation of signals. But also other useful software, like file browser, editors, audio players or the program “Scilab” for scientific calculations can run on the SDR. As programming IDE I used QtCreator, which offers the possibility to program directly on the Zynq instead of applying a cross compiler. Furthermore, the OS provides Ethernet, USB and HDMI interfaces for attaching network, monitor and input devices. During system start-up, a bootloader programs the FPGA with the bit stream containing the FPGA implementation.

Control Software

Tasks and Features

The tasks of the software for controlling the Panoradio is mainly to provide a GUI and to control the radio’s functionality. This control includes:

- setting the analog frontend path

- initializing the ADC and audio interface

- setting the DDC frequencies and filter properties

- determining amplifications for ADC and audio interfac

- reading IQ data from the DDCs for the FFT.

- calculating FFTs (including windowing, averaging, decimation etc.) for the waterfall displays

The software GUI has the following features:

- selection of the analog frontend (100 MHz, 70 cm or direct)

- AD converter input level monitoring

- AGC control after the ADC

- FFT averaging, update time and color scheme

- different modes for audio reception (bandwidth, binaural mode, spectrum inversion)

- monitoring of audio signal level and setting for audio amplifier

- Selection of a single audio receiver of the sum of both

- Control of digital test signals (sine, pulse, step)

- Monitoring of internal receiver states (signal and its spectrum at the different stages, setting of filters, LO etc) for debugging

Software Programming

The software for controlling the Panoradio is written in C++ and Qt. Qt provides a powerful framework for implementing a GUI and enhances C++ in many different useful ways. For the implementation of the waterfall display Qwt is used, a library for scientific applications, that provides e.g. various kinds of plots and sliders.

I have chosen C++ as programming language, because the execution speed of the software is critical. Interestingly, the bottleneck are not the FFTs or the communication with the IP cores, but the drawing routines for the waterfall plots. The Zynq does not have any graphics acceleration core, which could speed up the drawing process. However, Xilinx has realized this bottleneck and included graphics acceleration in the Zynq’s successors, the UltraScale MPSoC.

FFT Code

The processor calculates the various FFTs for the total five waterfall displays. The software implements a wrapper for the FFTW library (http://www.fftw.org/), a C library with fast FFT algorithms. The wrapper adds functions for applying a window, FFT averaging, converting to power scale in dBm and provides C++ style access to the FFTW lib.

Connecting the FPGA and the Processor

Basic information on how to connect FPGA and the processor can be found the in Zedboard / Zynq description. Basically, registers can be defined in the FPGA, that are directly mapped to some memory addresses in the processor, specified during FPGA design in Vivado. The processor can then read or write these FPGA registers by simply reading or writing to the memory address. The Panoradio uses a simple driver for that purpose based on the mmap command. This is not really “good design practice”, but for a tech demo it should be ok. It is also possible to write a simple Linux driver, that does it in a more elegant way.

Download my generic driver for Zynq IP Cores: IP_Driver.zip

FPGA Implementation

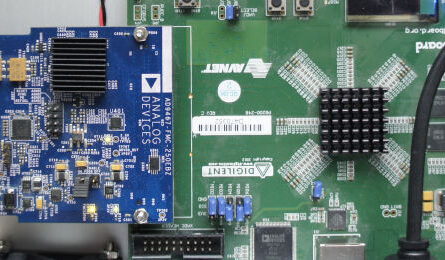

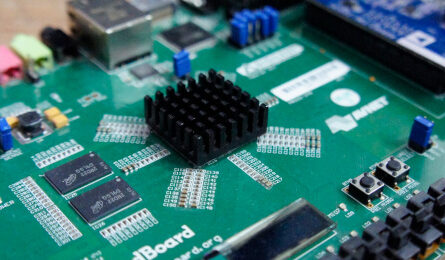

The high-speed digital processing parts of the Panoradio are implemented on the FPGA. The Zynq 7020 features a 7-series FPGA from Xilinx, which belongs to the mid-sized Zynq SoCs with in total 53.200 Look-Up tables and 106.400 flip-flops, 560 KB SRAM and 220 DSP slices.

The FPGA for the Panoradio design is less than 50% occupied. This quite low utilization would allow for even more complex DSP. However, I observed, that the Zedboard does not cope very well with high FPGA utilization in certain applications. Then it seems to have problems to deliver enough supply to the Zynq and operation becomes instable (also discussed in the official forum).

The main contributor to the radio’s complexity is the Waterfall DDC, because it operates for high sample frequencies and thus requires high parallelism. The second main contributor to the overall complexity is the interconnect between processor and FPGA, followed by the Audio demodulation and postprocessing.

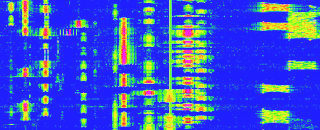

The floorplan shows the placement of the different SDR parts on the Zynq chip.